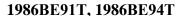

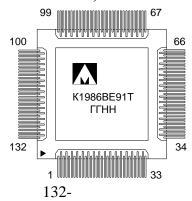

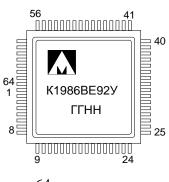

#### Микросхема 32-разрядного однокристального микро-ЭВМ с памятью Flash-типа 1986ВЕ9ху, К1986ВЕ9ху, К1986ВЕ9хуК K1986BE92QI, K1986BE92QC, 1986BE91H4, K1986BE91H4, 1986BE94H4, K1986BE94H4

1986BE92Y

1986BE92Y1

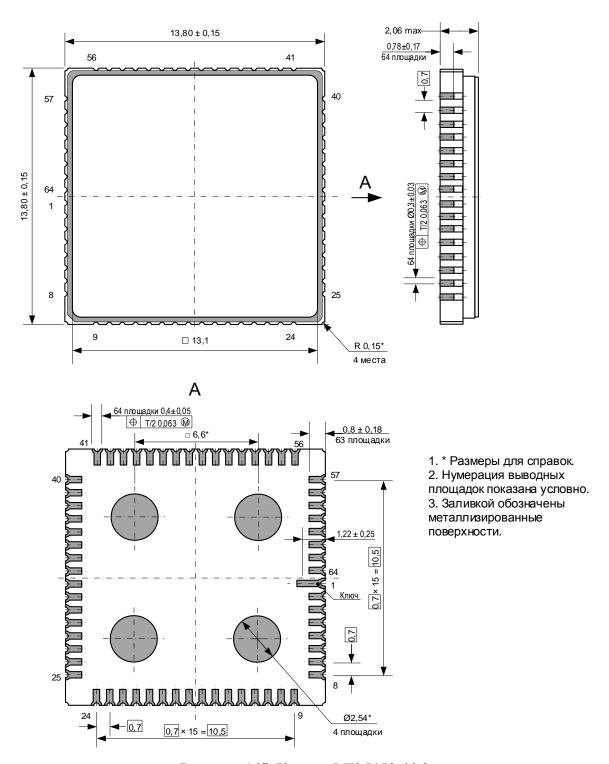

64-

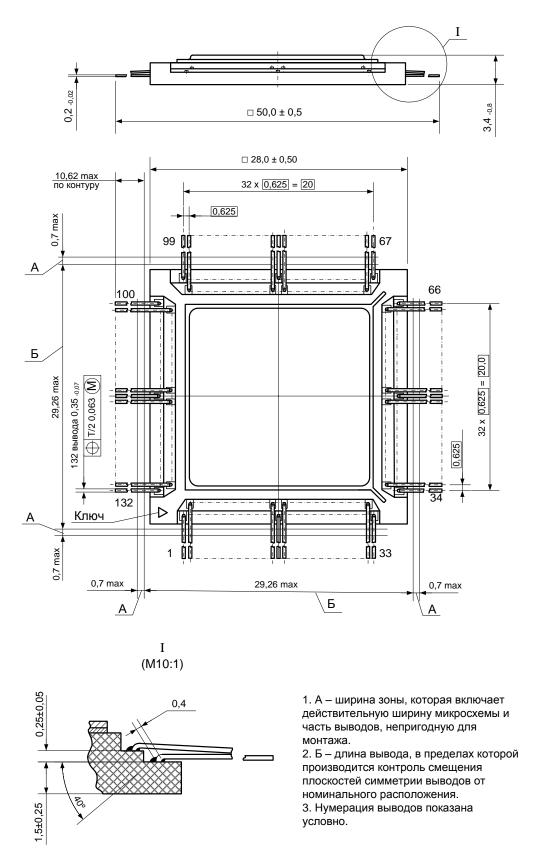

4229.132-3

K1986BE92Q

H18.64-1

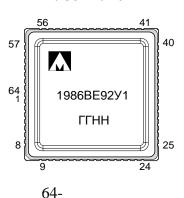

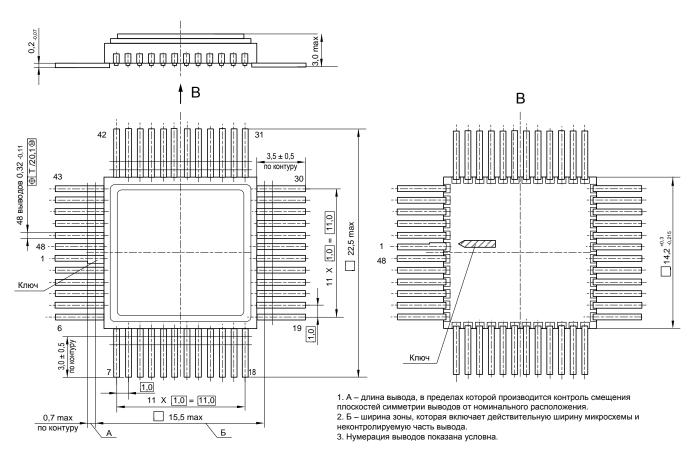

1986BE93Y 43 30 48 K1986BE93 ГГНН 6 18 48-

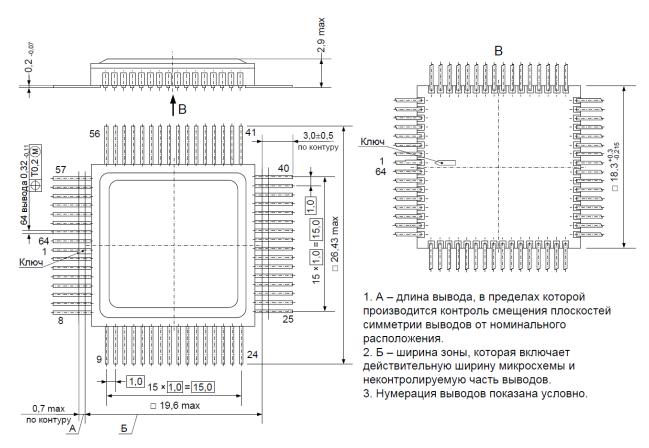

5153.64-2

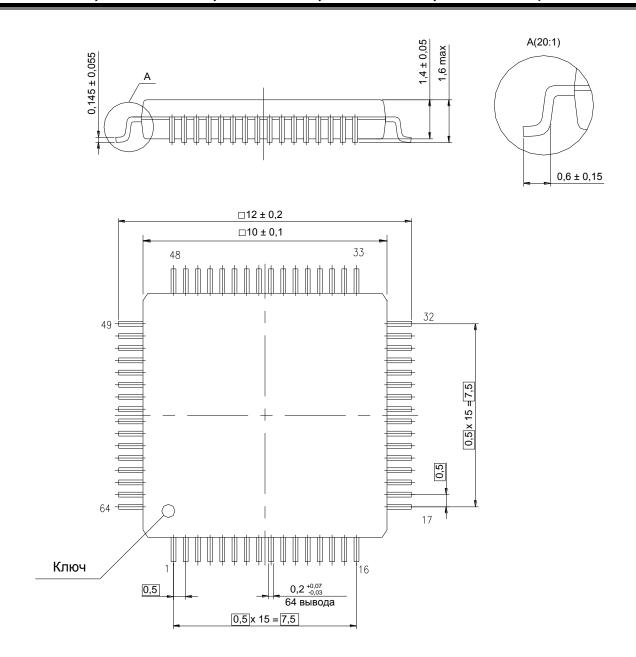

#### 1986ВЕ94Ф

LQFP64

16.48-1

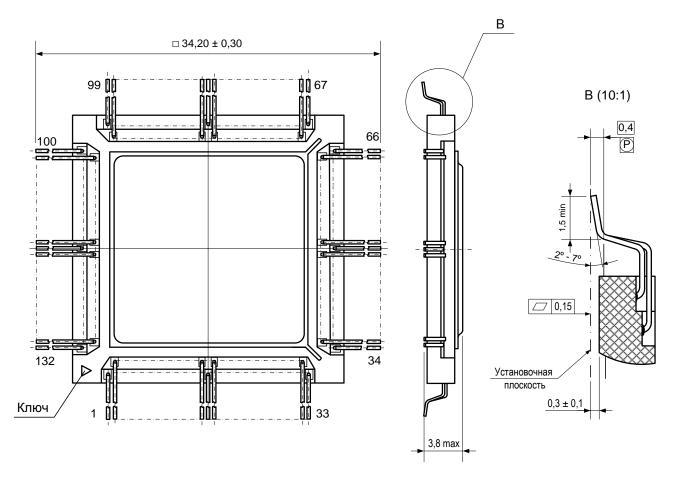

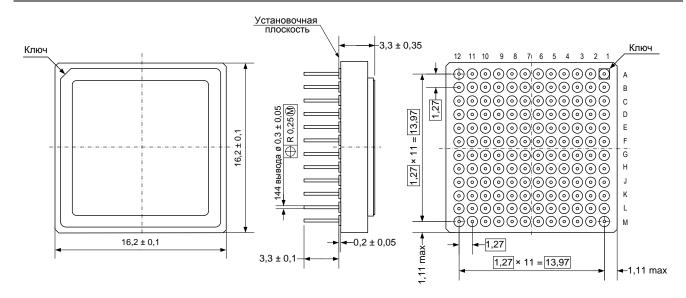

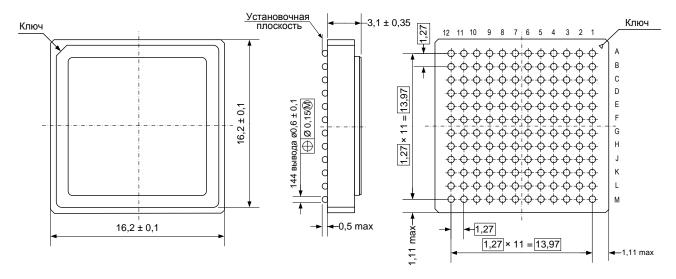

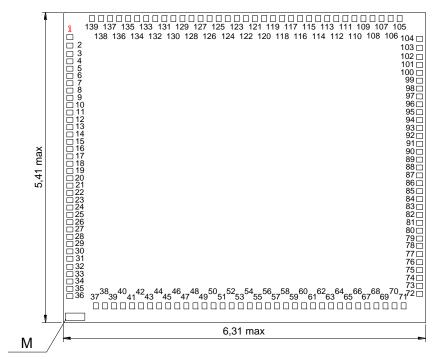

6109.144-

| Обозначение | Температурный диапазон |

|-------------|------------------------|

| 1986 9      | 60 ÷ 125 °             |

| 1986 9      | 60 ÷ 125 °             |

| 1986 9 K    | 0 ÷ 70 °               |

| 1986 9      | 0 ÷ 70 °               |

| 1986 9      | 0 ÷ 70 °               |

| 1986 92Q    | 0 ÷ 70 °               |

| 1986 92QI   | 40 ÷ 85 °              |

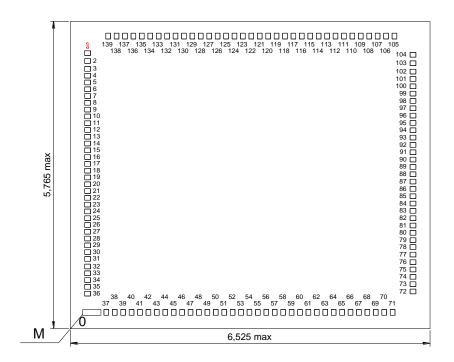

8307.144-

= 1, 2, 3, 4

```

К1986ВЕ9хуК

1986

9 y

К1986ВЕ9хГуК

1986

9 yK,

немонотонным

ΑЦП

|-1...+2|

1986

К1986ВЕ9хДуК

9 yK,

немонотонным ЦАП

|-1...+2|

K1986BE92QI

K1986BE92QC

1986

92 .

1986BE91H4, K1986BE91H4, 1986BE94H4, K1986BE94H4

Основные характеристики микроконтроллеров серии 1986ВЕ9х

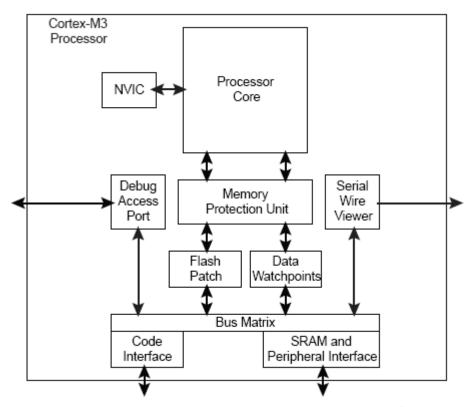

Ядро:

-ARM 32-

RISC-

Cortex<sup>™</sup>-M3

2.0,

80

1.25 DMIPS/

(Dhrystone 2.1)

MPU:

Память:

128

Flash-

32

, NAND Flash.

Питание и тактовая частота:

2,2 \div 3,6 ;

1,8

RC

40

2 \div 16

32

PLL

PLL

USB.

Режим пониженного энергопотребления:

Sleep, Deep Sleep Standby;

Аналоговые модули:

12-

16

);

12-

Периферия:

DMA

CAN

USB

Device Host;

UART, SPI, I2C;

16-

96

Отладочные интерфейсы:

SWD JTAG.

```

## Содержание

|    |              |            | 7   |

|----|--------------|------------|-----|

|    |              |            | 8   |

|    | -            |            | 9   |

|    |              |            | 10  |

|    |              |            | 26  |

|    |              |            |     |

|    |              |            |     |

|    |              |            |     |

|    |              |            |     |

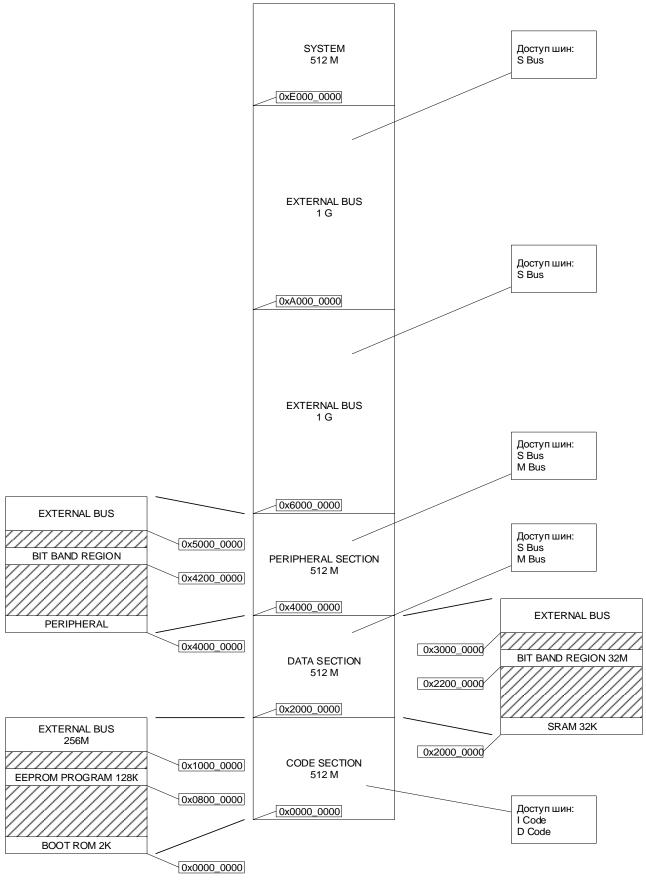

|    | CODE         |            | 37  |

|    | DATA         |            | 37  |

|    | PERIPHERAL   | <i>y</i>   | 37  |

|    | EXTERNAL R   | RAM        | 38  |

|    | SYSTEM       |            | 38  |

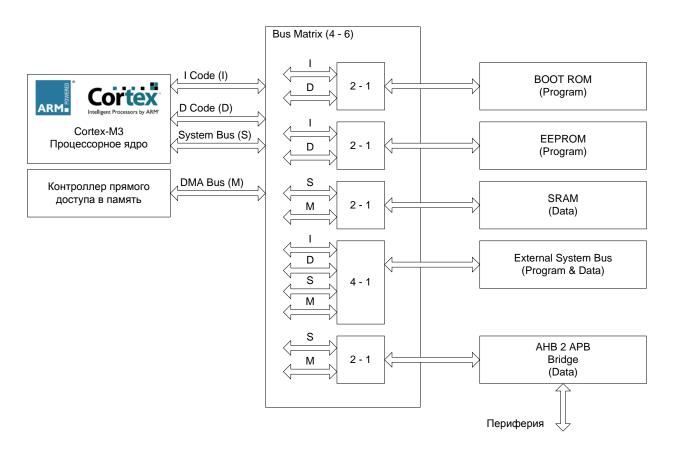

|    | BUS MATRIX   |            | 38  |

|    | BOOT ROM     |            | 38  |

|    | EEPROM       |            | 38  |

|    | SRAM         |            | 39  |

|    | ,            |            | 39  |

|    |              |            | 40  |

|    |              |            | 40  |

|    |              |            | 41  |

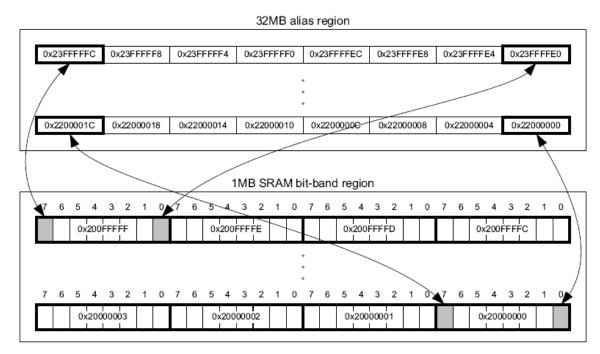

| Bi | t-band       |            | 43  |

|    |              |            | 44  |

|    |              |            | 46  |

|    |              |            | 47  |

|    |              |            | 49  |

| U. | ART          |            | 51  |

|    | Flash-       | MDR_EEPROM | 56  |

|    | Flash-       |            | 56  |

|    | Flash-       |            | 57  |

|    |              | Flash-     | 61  |

|    | ARM C        |            | 65  |

|    |              |            |     |

|    |              |            |     |

|    |              |            |     |

|    |              |            |     |

|    | ************ |            |     |

|    |              |            |     |

|    |              |            |     |

|    |              |            |     |

|    |              |            |     |

|    |              |            |     |

|    |              |            |     |

|    |              |            |     |

|    |              |            |     |

|    |              |            |     |

|    |              | k          |     |

|    | Systick      | A          | 172 |

| 12.1      | SysTick                           | 149 |

|-----------|-----------------------------------|-----|

| 12.2      |                                   | 152 |

| 13        | MPU                               | 153 |

| 13.1      | MPU                               | 154 |

| 13.2      | MPU                               | 163 |

| 14        | MDR_RST_CLK                       | 165 |

| 14.1      |                                   | 167 |

| 15        | MDR_BKP                           | 180 |

| 15.1      |                                   | 180 |

| 15.2      |                                   |     |

| 15.3      |                                   |     |

| 16        | - MDR_PORTx                       | 190 |

| 16.1      |                                   |     |

| 17        | MDR_POWER                         |     |

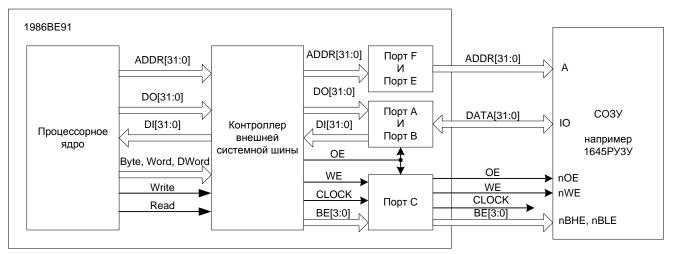

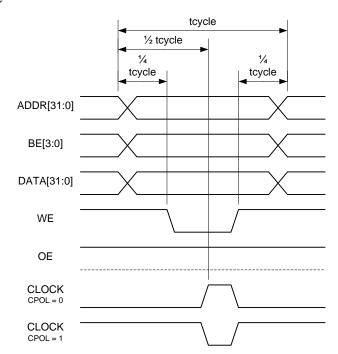

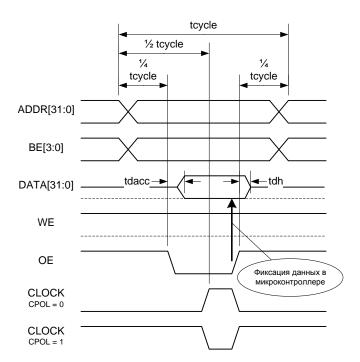

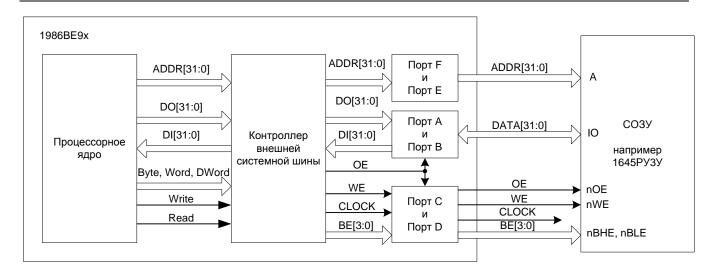

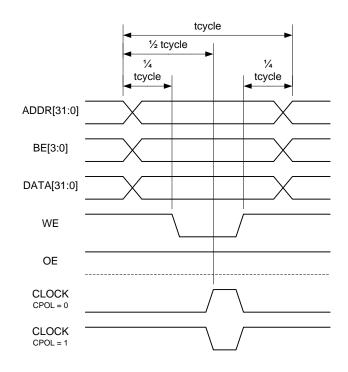

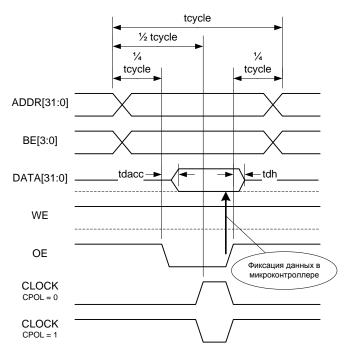

| 18        | MDR_EBC ( 1986 94 )               |     |

| 18.1      | , , , , , , , , , , , , , , , , , | 200 |

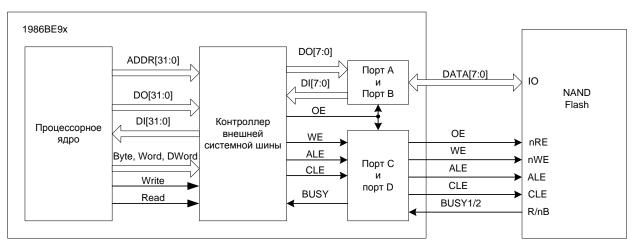

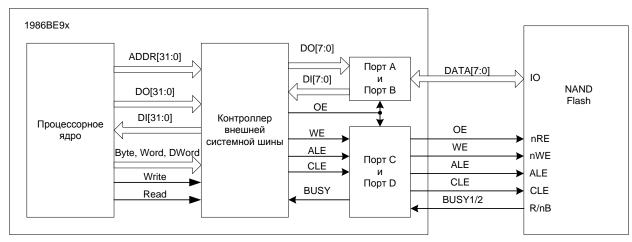

| 18.2      | NAND Flash-                       |     |

| 18.3      |                                   | 206 |

| 19        | MDR_EBC ( 1986 94 )               |     |

| 19.1      |                                   | 209 |

| 19.2      | NAND Flash-                       |     |

| 19.3      |                                   | 215 |

| 20        | MDR_USB                           |     |

| 20.1      | MDI_00D                           |     |

| 20.2      | USB /                             |     |

| 20.3      |                                   |     |

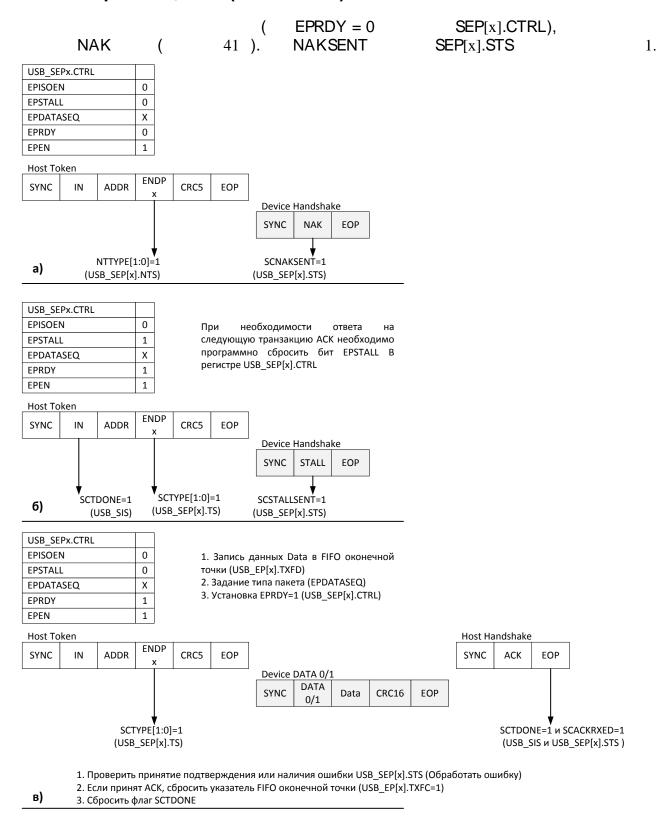

| 20.4      | IN (USB Device)                   |     |

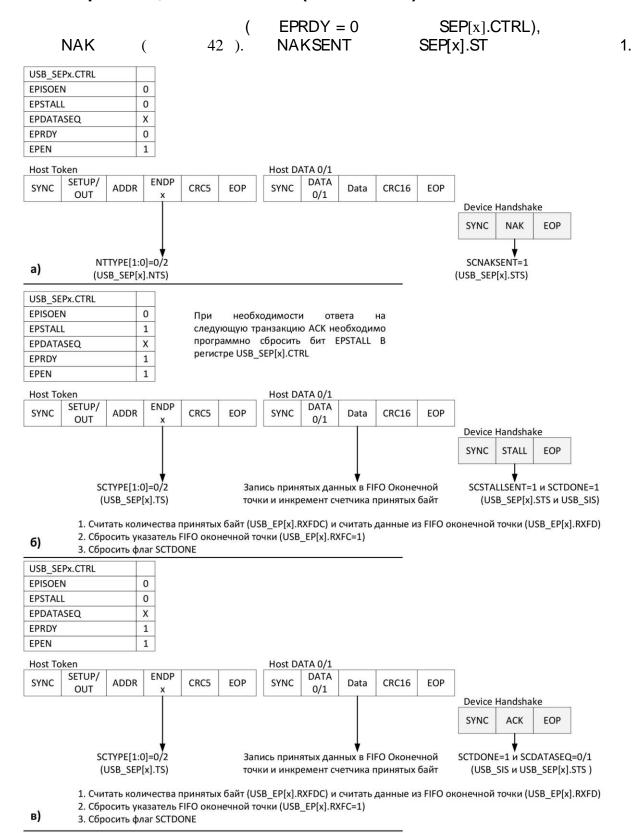

| 20.5      | SETUP/OUT (USB Device)            |     |

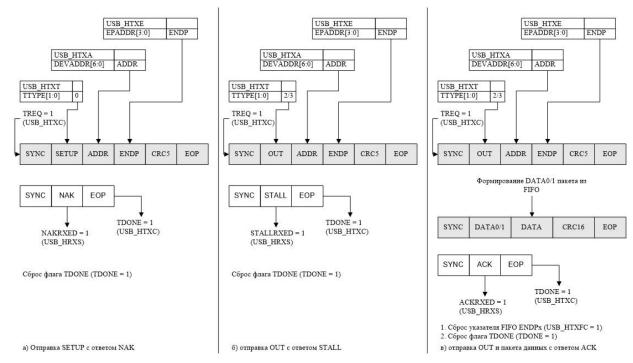

| 20.6      | SETUP/OUT (USB Host)              |     |

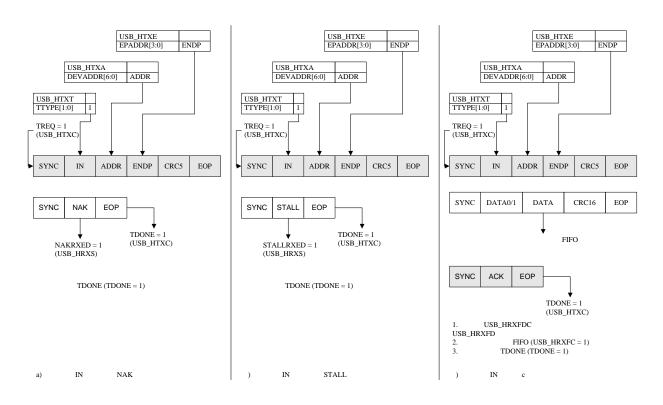

| 20.7      | IN (USB Host)                     |     |

| 20.7      | SOF (USB Host)                    |     |

| 20.9      | USB                               |     |

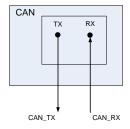

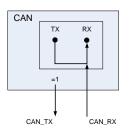

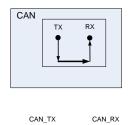

| 21        | MDR_CAN                           |     |

| 21.1      | MDK_C/IIV                         |     |

| 21.1      |                                   |     |

| 21.2      | (Data Frame)                      |     |

| 21.4      | (Data Farie)                      |     |

| 21.5      |                                   |     |

| 21.6      | Remote Transmit Request (RTR)     |     |

| 21.7      | Remote Transmit Request (RTR)     |     |

| 21.7      |                                   |     |

| 21.9      |                                   |     |

| 21.10     |                                   |     |

| 21.10     |                                   |     |

| 21.11     |                                   |     |

| 21.12     |                                   |     |

| 21.13     | CAN                               |     |

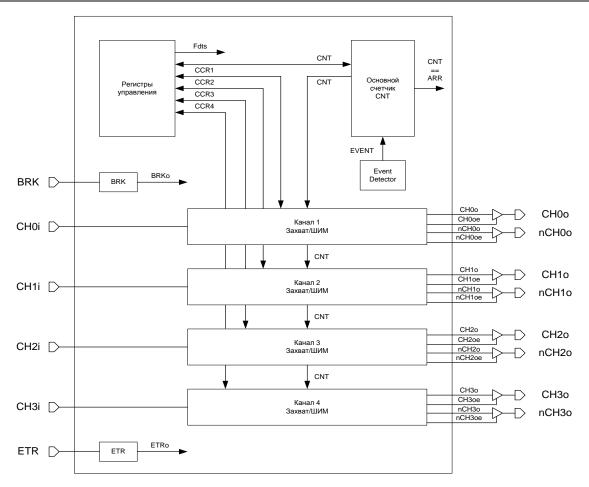

| 21.14     | MDR TIMERx                        |     |

| 22.1      | <u>-</u>                          |     |

| 22.1 22.2 |                                   |     |

| 22.2      |                                   |     |

| 44.9      |                                   | 404 |

| 22.4 |               |          | 280 |

|------|---------------|----------|-----|

| 22.4 |               |          |     |

| 22.6 |               |          |     |

| 22.7 | ••••••        |          |     |

| 23   | MDR ADC       |          |     |

| 23.1 | MDR_ADC       |          |     |

| 23.1 |               |          |     |

| 23.3 |               |          |     |

| 23.4 |               |          |     |

| 23.4 |               |          |     |

| 23.6 |               |          |     |

| 23.7 |               |          |     |

| 23.7 |               |          |     |

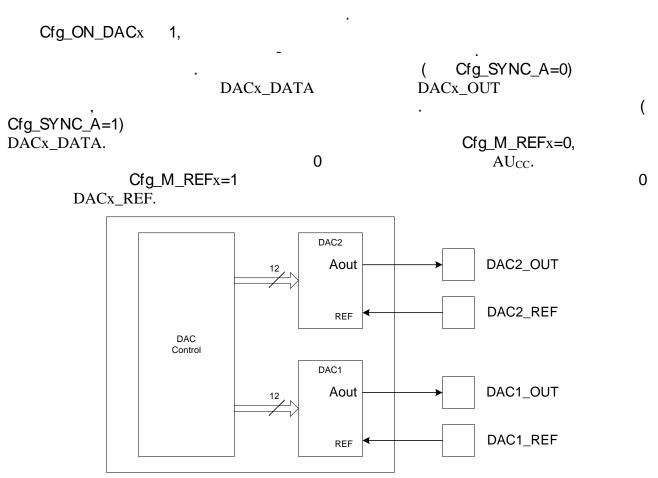

| 23.8 | MDP DAC       |          |     |

| 24.1 | MDR_DAC       |          |     |

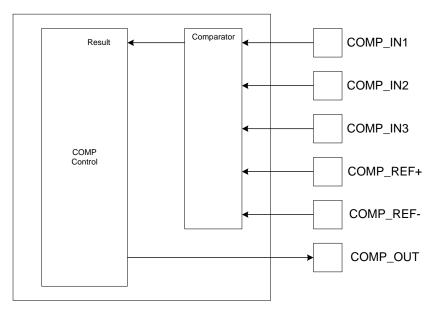

| 24.1 | ME            | OR COMP  |     |

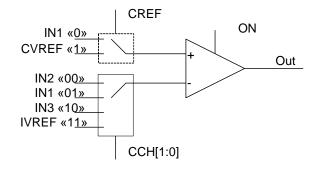

| 25.1 |               | _        |     |

|      |               |          |     |

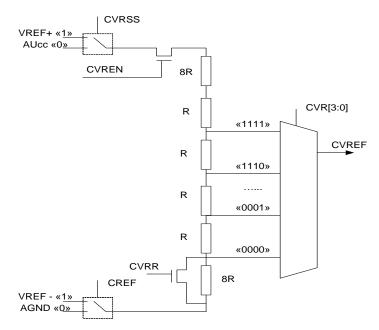

| 25.2 | С             |          |     |

| 25.3 | C             |          |     |

| 25.4 |               |          |     |

| 25.5 | MDD I2C       |          |     |

| 26   | _             |          |     |

| 26.1 |               |          |     |

| 26.2 |               |          |     |

| 26.3 |               |          |     |

| 26.4 |               |          |     |

| 26.5 |               |          |     |

| 26.6 | STOP          | 100      |     |

| 26.7 | MDD CCD       | I2C      |     |

| 27   | MDK_88P       | aab      |     |

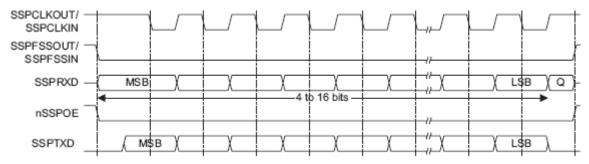

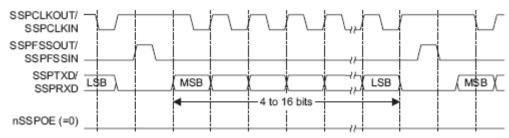

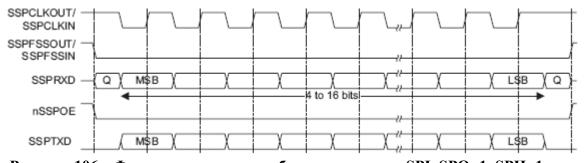

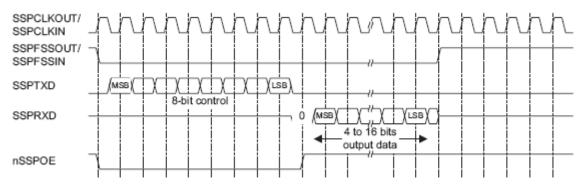

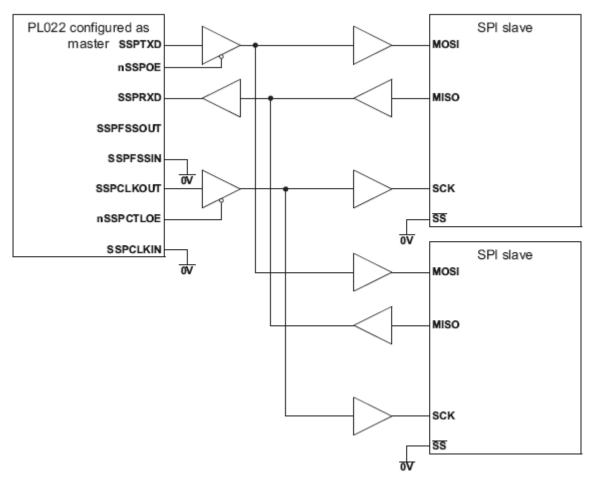

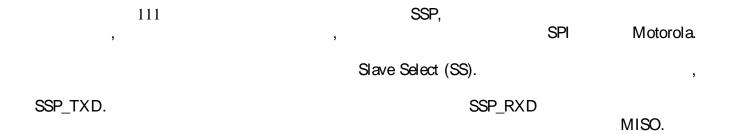

| 27.1 |               | SSP      |     |

| 27.2 | SF            |          |     |

| 27.3 | <del></del> - |          |     |

| 27.4 |               | icrowire |     |

| 27.5 |               | Si       |     |

| 27.6 | 55P           |          |     |

| 27.7 |               |          |     |

| 27.8 |               |          |     |

| 28   | <del>-</del>  |          |     |

| 28.1 |               |          |     |

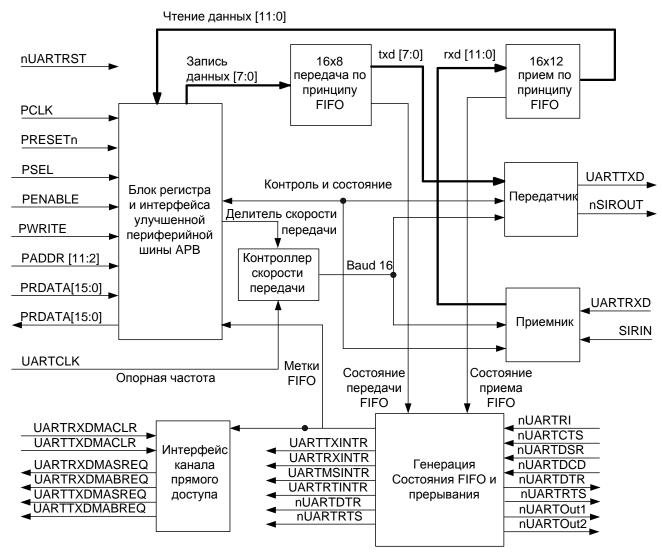

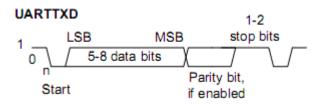

| 28.2 |               | IIADT    |     |

| 28.3 |               | UART     |     |

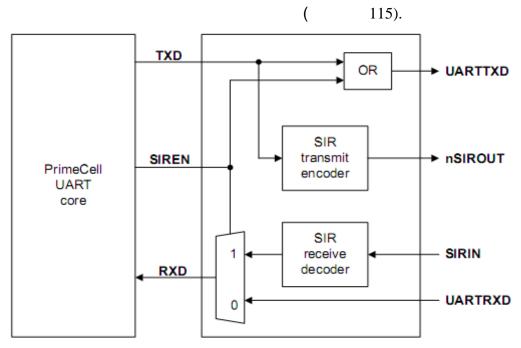

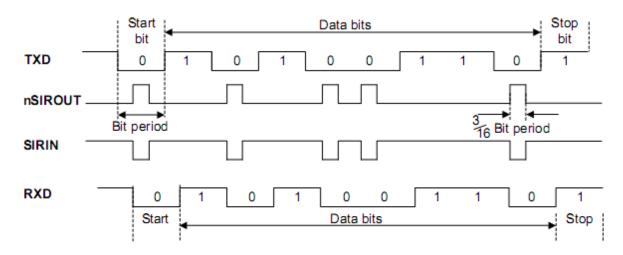

| 28.4 | HADT          | IrDA SIR |     |

| 28.5 |               |          |     |

| 28.6 | ••••          |          |     |

| 28.7 |               |          |     |

| 28.8 | ••••••        |          |     |

| 28.9 |               | MDD DMA  |     |

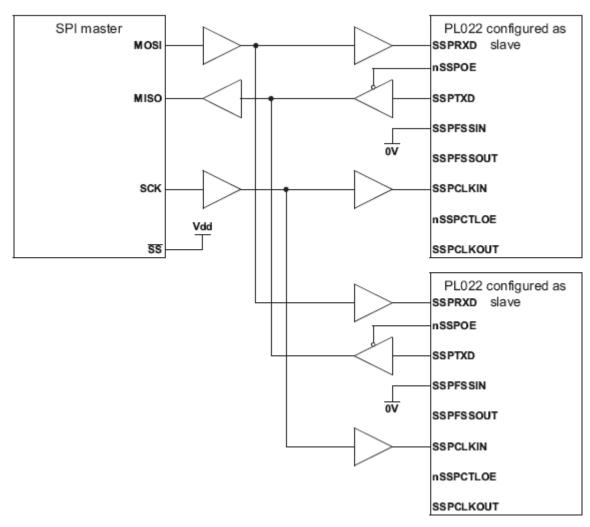

| 29   |               | MDR_DMA  |     |

| 29.1 |               | DMA      |     |

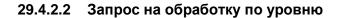

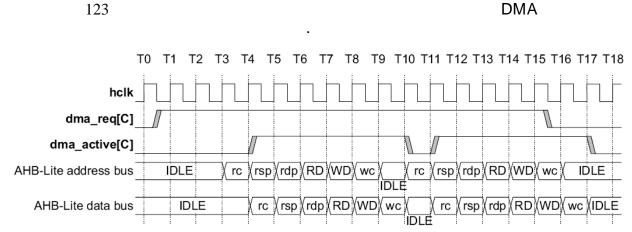

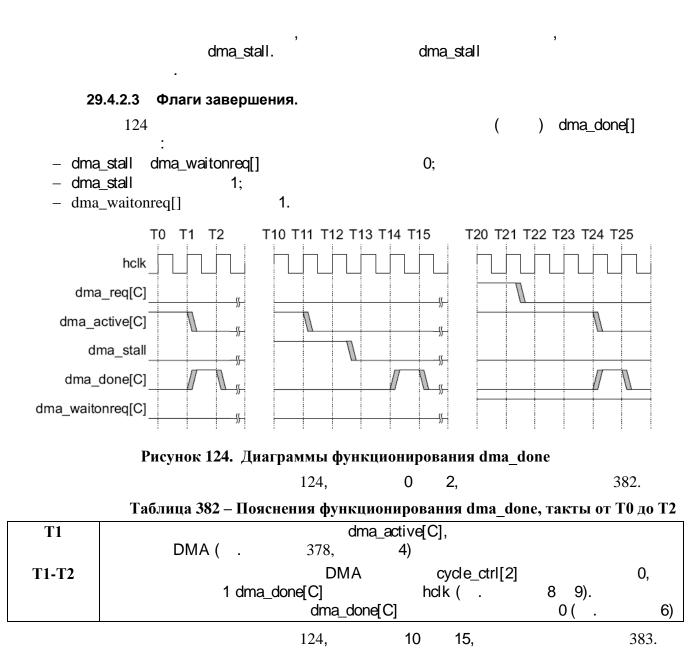

| 29.2 |               |          | 406 |

| 29.3 |       | 408 |

|------|-------|-----|

| 29.4 | DMA   | 411 |

| 29.5 |       | 433 |

| 29.6 | DMA   |     |

| 30   |       | 464 |

| 30.1 |       |     |

| 30.2 | (IRQ) |     |

| 30.3 |       |     |

| 30.4 |       |     |

| 30.5 |       |     |

| 30.6 |       |     |

| 30.7 |       | 471 |

| 30.8 |       | 473 |

| 31   | NVIC  | 476 |

| 31.1 |       | 477 |

| 31.2 | ,     | 482 |

| 31.3 |       | 482 |

| 31.4 |       | 483 |

| 32   |       |     |

| 32.1 |       |     |

| 33   |       | 501 |

| 33.1 |       | 501 |

| 34   |       | 506 |

| 35   |       | 509 |

| 36   |       | 511 |

| 37   |       | 515 |

| 38   |       |     |

| 39   |       | 531 |

| 40   |       | 532 |

|      |       |     |

#### 1 Введение

```

1986

1986

1986 92QC (

9x.

1986 9

92QI,

1986 9x),

RISC

ARM

Flash-

Cortex-M3,

128

32

80

USB

/ (Full Speed)

12

1,5

/ (Low Speed),

UART, SPI

I2C,

NAND Flash-

16-

4-

24-

0,5

12-

16

12-

RC

HSI (8 )

LSI (40

HSE

(2...16)

LSE (32

PLL

USB

)

DMA

```

1,8

3,6 .

2,2

© АО «ПКК Миландр»

## 2 Основные характеристики

,

Таблица 1 – Основные характеристики микроконтроллеров серии 1986ВЕ9х

|                         | 1986BE91T<br>1986BE94T | 1986ВЕ94Ф<br>1986ВЕ94Я | К1986ВЕ91Н4  | 1986BE92V<br>1986BE92V1<br>K1986BE92QI<br>K1986BE92QC | 1986BE93V |

|-------------------------|------------------------|------------------------|--------------|-------------------------------------------------------|-----------|

| Корпус                  | 132                    | 144                    |              | 64                                                    | 48        |

| Ядро                    |                        |                        | ARM Cortex-M | 13                                                    |           |

| ПЗУ                     |                        |                        | 128 Flas     | sh                                                    |           |

| ОЗУ                     |                        |                        | 32           |                                                       |           |

| Питание                 |                        |                        | 2,23,6       |                                                       |           |

| Частота                 |                        |                        | 80           |                                                       |           |

| USER IO                 | 96                     | 96                     | 96           | 43                                                    | 30        |

| USB                     | D                      | evice Host FS          | S ( 12 /     | ) PH                                                  | ΙΥ        |

| UART                    | 2                      | 2                      | 2            | 2                                                     | 2         |

| CAN                     | 2                      | 2                      | 2            | 2                                                     | 2         |

| SPI                     | 2                      | 2                      | 2            | 2                                                     | 1         |

| <b>I2</b> C             | 1                      | 1                      | 1            | 1                                                     | -         |

| 2 х 12-разрядных<br>АЦП | 16                     | 16                     | 16           | 8                                                     | 4         |

| ЦАП<br>12 разрядов      | 2                      | 2                      | 2            | 1                                                     | 1         |

| Компаратор              | 3                      | 3                      | 3            | 2                                                     | 2         |

| Внешняя шина            | 32                     | 32                     | 32           | 8                                                     | -         |

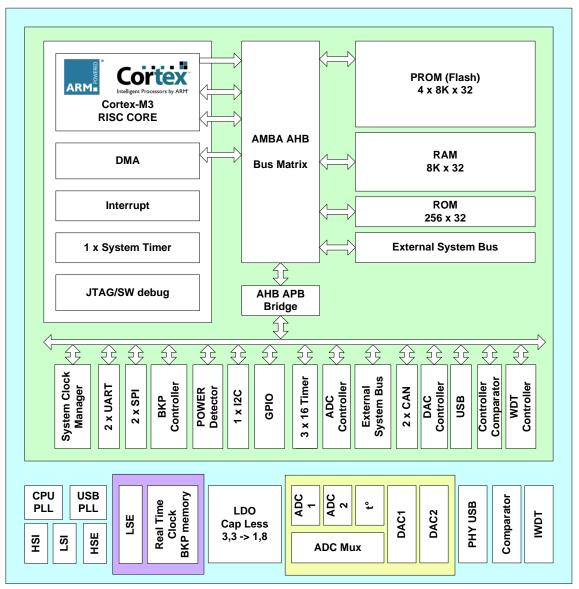

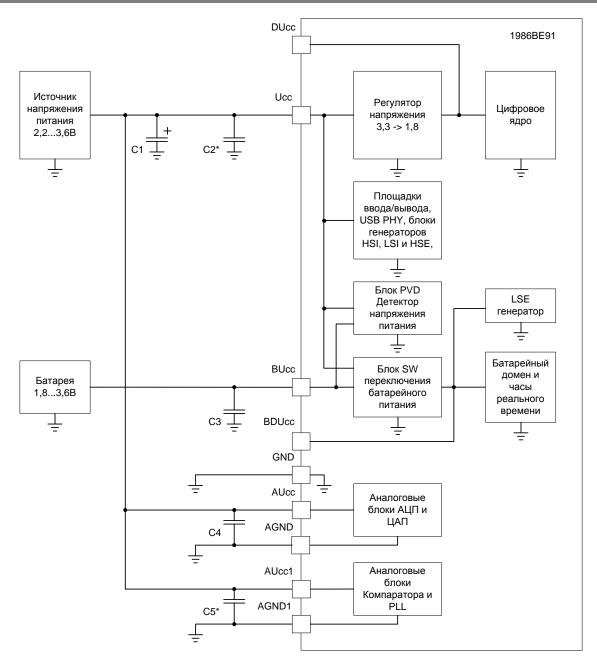

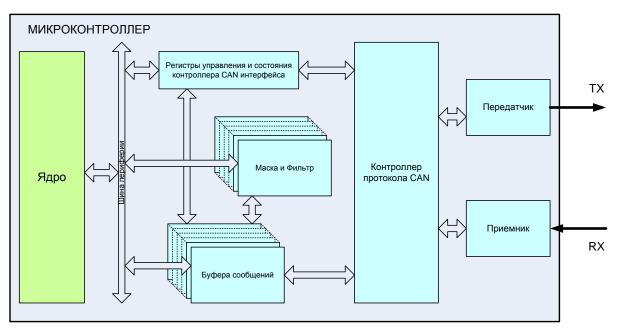

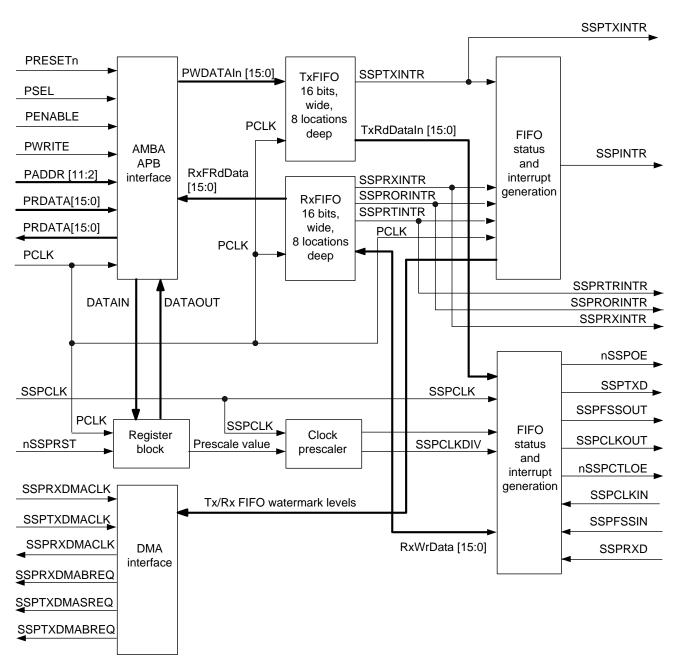

## 3 Структурная блок-схема микросхемы

Рисунок 1. Структурная блок-схема микроконтроллера 1986ВЕ9ху

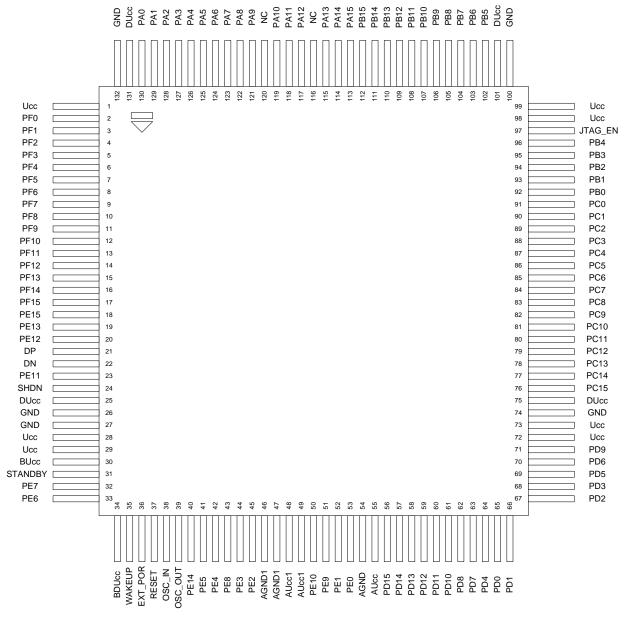

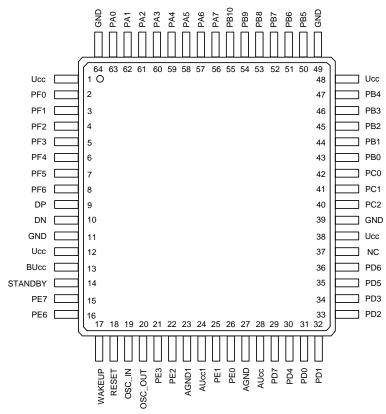

#### 4 Описание выводов

Таблица 2 – Описание выводов микроконтроллеров серии 1986BE9x в корпусах 4229.132-3, H18.64-1B, H16.48-1B, MK 5153.64-2, LQFP64

|                | Контактная |            |     | ип корпу  |                 |                |              |                  | 5, мих 3133.04-2<br>5ные функции в |                       |

|----------------|------------|------------|-----|-----------|-----------------|----------------|--------------|------------------|------------------------------------|-----------------------|

| Вывод          | площадка   | 4229.132-3 |     | H16.48-1B | MK<br>5153.64-2 | LQFP64         | Аналог.      | Основ.           | Альтер.                            | Переопр.              |

|                | кристалла  |            |     |           |                 | _ ~            | 111111111111 | o those          | 1 and 1 opt                        | Переопр               |

| PA0            | 137        | 130        | 55  | 41        | 55              | <b>рт А</b> 63 | _            | DATA0            | EXT_INT1                           | 1                     |

| PA1            | 136        | 129        | 54  | 40        | 54              | 62             | _            | DATA1            | TMR1_CH1                           | TMR2_CH1              |

| PA2            | 135        | 129        | 53  | 39        | 53              | 61             | -            | DATA1<br>DATA2   | TMR1_CH1N                          | TMR2_CH1N             |

|                |            |            |     |           | 52              |                |              |                  |                                    |                       |

| PA3            | 134        | 127        | 52  | 38        |                 | 60             | -            | DATA3            | TMR1_CH2                           | TMR2_CH2              |

| PA4            | 133        | 126        | 51  | 37        | 51              | 59             | -            | DATA4            | TMR1_CH2N                          | TMR2_CH2N             |

| PA5            | 132        | 125        | 50  | 36        | 50              | 58             | -            | DATA5            | TMR1_CH3                           | TMR2_CH3              |

| PA6            | 131        | 124        | 49  | 35        | 49              | 57             | -            | DATA6            | CAN1_TX                            | UART1_RXD             |

| PA7            | 130        | 123        | 48  | 34        | 48              | 56             | -            | DATA7            | CAN1_RX                            | UART1_TXD             |

| PA8            | 129        | 122        | -   | -         | -               | -              | -            | DATA8            | TMR1_CH3N                          | TMR2_CH3N             |

| PA9            | 128        | 121        | -   | -         | -               | -              | -            | DATA9            | TMR1_CH4                           | TMR2_CH4              |

| PA10           | 125        | 119        | -   | -         | -               | -              | -            | DATA10           | nUART1DTR                          | TMR2_CH4N             |

| PA11           | 124        | 118        | -   | -         | -               | -              | -            | DATA11           | nUART1RTS                          | TMR2_BLK              |

| PA12           | 123        | 117        | -   | -         | -               | -              | -            | DATA12           | nUART1RI                           | TMR2_ETR              |

| PA13           | 122        | 115        | -   | -         | -               | -              | -            | DATA13           | nUART1DCD                          | TMR1_CH4N             |

| PA14           | 121        | 114        | -   | -         | -               | -              | -            | DATA14           | nUART1DSR                          | TMR1_BLK              |

| PA15           | 120        | 113        | -   | -         | -               | -              | -            | DATA15           | nUART1CTS                          | TMR1_ETR              |

|                | 1          |            |     |           | По              | рт В           |              | I= . =           |                                    |                       |

| PB0            | 97         | 92         | 35  | 25        | 35              | 43             | -            | DATA16           | TMR3_CH1                           | UART1_TXD             |

| JA_TDO         |            |            |     |           |                 | _              |              |                  |                                    |                       |

| PB1            | 98         | 93         | 36  | 26        | 36              | 44             | -            | DATA17           | TMR3_CH1N                          | UART2_RXD             |

| JA_TMS         |            |            |     |           |                 |                |              |                  |                                    |                       |

| PB2            | 99         | 94         | 37  | 27        | 37              | 45             | -            | DATA18           | TMR3_CH2                           | CAN1_TX               |

| JA_TCK         | 100        | 0.5        | 20  | 20        |                 |                |              | D 4 E 4 10       | The Change                         | CANA DV               |

| PB3            | 100        | 95         | 38  | 28        | 38              | 46             | -            | DATA19           | TMR3_CH2N                          | CAN1_RX               |

| JA_TDI         | 101        | 0.6        | 20  | 20        |                 |                |              | D 4 T 4 20       | TNAD 2 DI IZ                       | TIMBA ETT             |

| PB4            | 101        | 96         | 39  | 29        | 39              | 47             | -            | DATA20           | TMR3_BLK                           | TMR3_ETR              |

| JA_TRST<br>PB5 | 107        | 102        | 42  | 32        | 42              | 50             |              | DATAGI           | LIADTI TVD                         | TMD2 CH2              |

| PB6            | 107        | 102        | 42  | 33        | 43              | 51             | -            | DATA21<br>DATA22 | UART1_TXD<br>UART1_RXD             | TMR3_CH3<br>TMR3_CH3N |

| PB7            |            |            | 43  |           |                 | 52             | -            |                  | nSIROUT1                           |                       |

|                | 109        | 104        |     | -         | 44              | 53             | -            | DATA24           |                                    | TMR3_CH4              |

| PB8            | 110        | 105        | 45  | -         | 45              |                | -            | DATA24           | COMP_OUT                           | TMR3_CH4N             |

| PB9            | 111        | 106        | 46  | -         | 46              | 54             | -            | DATA25           | nSIRIN1                            | EXT_INT4              |

| PB10           | 112        | 107        | 47  | -         | 47              | 55             | -            | DATA26           | EXT_INT2                           | nSIROUT1              |

| PB11           | 113        | 108        | -   | -         | -               | -              | -            | DATA27           | EXT_INT1                           | COMP_OUT              |

| PB12           | 114        | 109        | -   | -         | -               | -              | -            | DATA28           | SSP1_FSS                           | SSP2_FSS              |

| PB13           | 115        | 110        | -   | -         | -               | -              | -            | DATA29           | SSP1_CLK                           | SSP2_CLK              |

| PB14           | 116        | 111        | -   | -         | -               | -              | -            | DATA30           | SSP1_RXD                           | SSP2_RXD              |

| PB15           | 119        | 112        | -   | -         | -               | -              | -            | DATA31           | SSP1_TXD                           | SSP2_TXD              |

| D.C.O.         | 0.6        | 0.1        | 2.4 | 22        |                 | рт С           |              | DE A DAZA        | CCT 1                              | aaba Eaa              |

| PC0            | 96         | 91         | 34  | 23        | 34              | 42             | -            | READY*           | SCL1                               | SSP2_FSS              |

| PC1            | 95         | 90         | 33  | -         | 33              | 41             | -            | OE               | SDA1                               | SSP2_CLK              |

| PC2            | 94         | 89         | 31  | -         | 31              | 40             | -            | WE               | TMR3_CH1                           | SSP2_RXD              |

| PC3            | 93         | 88         | -   | -         | -               | -              | -            | BE0              | TMR3_CH1N                          | SSP2_TXD              |

| PC4            | 92         | 87         | -   | -         | -               | -              | -            | BE1              | TMR3_CH2                           | TMR1_CH1              |

| PC5            | 91         | 86         | -   | -         | -               | -              | -            | BE2              | TMR3_CH2N                          | TMR1_CH1N             |

| PC6            | 90         | 85         | -   | -         | -               | -              | -            | BE3              | TMR3_CH3                           | TMR1_CH2              |

| PC7            | 89         | 84         | -   | -         | -               | -              | -            | CLOCK            | TMR3_CH3N                          | TMR1_CH2N             |

| PC8            | 88         | 83         | -   | -         | -               | -              | -            | CAN1_TX          | TMR3_CH4                           | TMR1_CH3              |

| PC9            | 87         | 82         | -   | -         | -               | -              | -            | CAN1_RX          | TMR3_CH4N                          | TMR1_CH3N             |

|                | Контактная            |    | T         | ип корпу  | ca              |        | вывода        |               |           |           |

|----------------|-----------------------|----|-----------|-----------|-----------------|--------|---------------|---------------|-----------|-----------|

| Вывод          | площадка<br>кристалла |    | H18.64-1B | H16.48-1B | MK<br>5153.64-2 | LQFP64 | Аналог.       | Основ.        | Альтер.   | Переопр.  |

| PC10           | 86                    | 81 | -         | -         | -               | -      | -             | -             | TMR3_ETR  | TMR1_CH4  |

| PC11           | 85                    | 80 | -         | -         | -               | -      | -             | -             | TMR3_BLK  | TMR1_CH4N |

| PC12           | 84                    | 79 | -         | -         | -               | -      | -             | -             | EXT_INT2  | TMR1_ETR  |

| PC13           | 83                    | 78 | -         | -         | -               | -      | -             | -             | EXT_INT4  | TMR1_BLK  |

| PC14           | 82                    | 77 | -         | -         | -               | -      | -             | -             | SSP2_FSS  | CAN2_RX   |

| PC15           | 81                    | 76 | -         | -         | -               | -      | -             | -             | SSP2_RXD  | CAN2_TX   |

|                |                       |    |           |           | По              | рт D   |               |               |           |           |

| PD0<br>JB_TMS  | 70                    | 65 | 23        | 17        | 23              | 31     | EF+           | N             | UART2_RXD | TMR3_CH1  |

| PD1<br>JB_TCK  | 71                    | 66 | 24        | 18        | 24              | 32     | EF-           | _             | UART2_TXD | TMR3_CH1N |

| PD2<br>JB_TRST | 72                    | 67 | 25        | 19        | 25              | 33     | ADC2          | BUSY1         | SSP2_RXD  | TMR3_CH2  |

| PD3<br>JB_TDI  | 73                    | 68 | 26        | 20        | 26              | 34     | ADC3          | -             | SSP2_FSS  | TMR3_CH2N |

| PD4<br>JB_TDO  | 69                    | 64 | 22        | -         | 22              | 30     | ADC4          | TMR1_ETR      |           | TMR3_BLK  |

| PD5            | 74                    | 69 | 27        | -         | 27              | 35     | ADC5          | CLE           | SSP2_CLK  | TMR2_ETR  |

| PD6            | 75                    | 70 | 28        | -         | 28              | 36     | ADC6          | ALE           | SSP2_TXD  | TMR2_BLK  |

| PD7            | 68                    | 63 | 21        | -         | 21              | 29     | ADC7          | TMR1_BL<br>K  | nSIRIN2   | UART1_RXD |

| PD8            | 67                    | 62 | -         | -         | -               | -      | ADC8          | N             | TMR2_CH1  | UART1_TXD |

| PD9            | 76                    | 71 | -         | ı         | ı               | ı      | ADC9          | CAN2_TX       | TMR2_CH1N | SSP1_FSS  |

| PD10           | 66                    | 61 | -         | -         | -               | -      | ADC10         | TMR1_CH2      | TMR2_CH2  | SSP1_CLK  |

| PD11           | 65                    | 60 | -         | -         | -               | -      | ADC11         | TMR1_CH2<br>N | TMR2_CH2N | SSP1_RXD  |

| PD12           | 64                    | 59 | -         | -         | -               | -      | ADC12         | TMR1_CH3      | TMR2_CH3  | SSP1_TXD  |

| PD13           | 63                    | 58 | -         | -         | -               | -      | ADC13         | TMR1_CH3<br>N | TMR2_CH3N | CAN1_TX   |

| PD14           | 62                    | 57 | -         | -         | -               | -      | ADC14         | TMR1_CH4      | TMR2_CH4  | CAN1_RX   |

| PD15           | 61                    | 56 | -         | -         | -               | -      | ADC15         | CAN2_RX       | BUSY2     | EXT_INT3  |

|                |                       |    |           |           | По              | рт Е   |               |               |           |           |

| PE0            | 56                    | 53 | 18        | 14        | 18              | 26     | DAC2_O<br>UT  | ADDR16        | TMR2_CH1  | CAN1_RX   |

| PE1            | 55                    | 52 | 17        | -         | 17              | 25     | DAC2_R<br>EF  | ADDR17        | TMR2_CH1N | CAN1_TX   |

| PE2            | 48                    | 45 | 14        | 11        | 14              | 22     | COMP_I<br>N1  |               | TMR2_CH3  | TMR3_CH1  |

| PE3            | 47                    | 44 | 13        | 10        | 13              | 21     | COMP_I<br>N2  |               | TMR2_CH3N | TMR3_CH1N |

| PE4            | 45                    | 42 | -         | -         | -               | -      | COMP_R<br>EF+ |               | TMR2_CH4N | TMR3_CH2  |

| PE5            | 44                    | 41 | -         | -         | -               | -      | COMP_R<br>EF- |               | TMR2_BLK  | TMR3_CH2N |

| PE6            | 36                    | 33 | 8         | 6         | 8               | 16     | OSC_IN3       | ADDR22        | CAN2_RX   | TMR3_CH3  |

| PE7            | 35                    | 32 | 7         | -         | 7               | 15     | OSC_OU<br>T32 | ADDR23        | CAN2_TX   | TMR3_CH3N |

| PE8            | 46                    | 43 | -         | -         | -               | -      | N3            | ADDR24        | TMR2_CH4  | TMR3_CH4  |

| PE9            | 54                    | 51 | -         | -         | -               | -      | DAC1_O<br>UT  | ADDR25        | TMR2_CH2  | TMR3_CH4N |

| PE10           | 53                    | 50 | -         | -         | -               | -      | DAC1_R<br>EF  | ADDR26        | TMR2_CH2N | TMR3_ETR  |

| PE11           | 26                    | 23 | -         | -         | -               | -      | -             | ADDR27        | nSIRIN1   | TMR3_BLK  |

| PE12           | 21                    | 20 | _         | _         | _               | -      | _             | ADDR28        | SSP1_RXD  | UART1_RXD |

|                   | Контактная               |                          | Т              | ип корпус      | ca               |                     | Д          | ополнител            | ьные функции і | вывода    |

|-------------------|--------------------------|--------------------------|----------------|----------------|------------------|---------------------|------------|----------------------|----------------|-----------|

| Вывод             | площадка<br>кристалла    | 4229.132-3               | H18.64-1B      |                | MK<br>5153.64-2  | LQFP64              | Аналог.    | Основ.               | Альтер.        | Переопр.  |

| PE13              | 20                       | 19                       | -              | -              | -                | 1                   | -          | ADDR29               | SSP1_FSS       | UART1_TXD |

| PE14              | 43                       | 40                       | -              | -              | -                | -                   | -          | ADDR30               | TMR2_ETR       | SCL1      |

| PE15              | 19                       | 18                       | -              | -              | -                | -                   | -          | ADDR31               | EXT_INT3       | SDA1      |

|                   | ı                        | 1                        | ı              |                |                  | рт F                | T          | 1                    |                | 1         |

| PF0               | 3                        | 2                        | 58             | 44             | 58               | 2                   | -          | ADDR0                | SSP1_TXD       | UART2_RXD |

| PF1               | 4                        | 3                        | 59             | 45             | 59               | 3                   | -          | ADDR1                | SSP1_CLK       | UART2_TXD |

| PF2               | 5                        | 4                        | 60             | 46             | 60               | 4                   |            | ADDR2                | SSP1_FSS       | CAN2_RX   |

| PF3               | 6                        | 5                        | 61             | 47             | 61               | 5                   | -          | ADDR3                | SSP1_RXD       | CAN2_TX   |

| PF4<br>MODE[0]    | 7                        | 6                        | 62             | 48             | 62               | 6                   | -          | ADDR4                | -              | -         |

| PF5<br>MODE[1]    | 8                        | 7                        | 63             | 1              | 63               | 7                   | -          | ADDR5                | -              | -         |

| PF6<br>MODE[2]    | 9                        | 8                        | 64             | -              | 64               | 8                   | -          | ADDR6                | TMR1_CH1       | -         |

| PF7               | 10                       | 9                        | -              | -              | -                | -                   | -          | ADDR7                | TMR1_CH1N      | TMR3_CH1  |

| PF8               | 11                       | 10                       | -              | -              | -                | -                   | -          | ADDR8                | TMR1_CH2       | TMR3_CH1N |

| PF9               | 12                       | 11                       | -              | -              | -                | -                   | -          | ADDR9                | TMR1_CH2N      | TMR3_CH2  |

| PF10              | 13                       | 12                       | -              | -              | -                | -                   | -          | ADDR10               | TMR1_CH3       | TMR3_CH2N |

| PF11              | 14                       | 13                       | -              | -              | -                | -                   | -          | ADDR11               | TMR1_CH3N      | TMR3_ETR  |

| PF12              | 15                       | 14                       | -              | -              | -                | -                   | -          | ADDR12               | TMR1_CH4       | SSP2_FSS  |

| PF13              | 16                       | 15                       | -              | -              | -                | -                   |            | ADDR13               | TMR1_CH4N      | SSP2_CLK  |

| PF14              | 17                       | 16                       | -              | -              | -                | -                   | -          | ADDR14               | TMR1_ETR       | SSP2_RXD  |

| PF15              | 18                       | 17                       | -              | -              | -                | -                   | -          | ADDR15               | TMR1_BLK       | SSP2_TXD  |

| DECET             | 40                       | 37                       | 10             |                | истемно          | управл              | ение       |                      |                |           |

| RESET             | 40                       | 37                       | 10             | 7              | 10               | 18                  | 0 –<br>1 – |                      |                |           |

| WAKEUP            | 38                       | 35                       | 9              | -              | 9                | 17                  | 0 –<br>1 – | :                    | S<br>StandBy   | tandby    |

| STANDBY           | 34                       | 31                       | 6              | -              | 6                | 14                  | 0 –        | Standby              | StandBy        |           |

| OCC. IN           | 4.1                      | 20                       | 1.1            | 0              | 1.1              | 10                  | 1 –        | Her                  | StandBy        |           |

| OSC_IN            | 41                       | 38                       | 11             | 8              | 11               | 19                  |            | HSE                  |                |           |

| OSC_OUT           | 42                       | 39                       | 12             | 9              | 12<br>UCD        | 20                  |            | HS                   | E              |           |

| DP                | 22                       | 21                       | 1              | 2              | 1 USB 11         | <b>нтерфей</b><br>9 |            | B D+                 |                |           |

| DN                | 25                       | 22                       | 2              | 3              | 2                | 10                  |            | <u>в D</u> +<br>В D- |                |           |

| DIV               | 23                       | 22                       |                | 3              |                  | гание               | 05.        | <u> Б Б-</u>         |                |           |

| UCC               | 1,2,31,32,<br>77,78,103, | 72,73,                   | 4,29,40,<br>57 | 5,21,30,4<br>3 | 4, 29,<br>40, 57 | 1, 12,<br>38, 48    |            | 2,2                  | 23,6           |           |

| AU <sub>CC</sub>  | 104<br>59,60             | 98,99<br>55              | 20             | 16             | 20               | 28                  | 0.4.00     |                      | , Cor          | mparator  |

| AU <sub>CC1</sub> | 51,52                    | 48,49                    | 16             | 13             | 16               | 24                  | 2,43,6     | I                    | PLL 2,23,6     |           |

| BU <sub>CC</sub>  | 33                       | 30                       | 5              | -              | 5                | 13                  |            | 1                    | .83,6          |           |

| GND               | 29,30,79,<br>105,139     | 26,27,<br>74,100,<br>132 | 3,30,41,<br>56 | 4,22,31,4      | 3, 30,<br>41, 56 | 11, 39,<br>49, 64   |            |                      |                |           |

| AGND              | 57,58                    | 54                       | 19             | 15             | 19               | 27                  |            |                      |                |           |

| AGND1             | 49,50                    | 46,47                    | 15             | 12             | 15               | 23                  |            |                      |                |           |

| DUCC              | 28,80,106,<br>138        |                          |                | -              | -                | -                   |            |                      |                |           |

|                   |                          | , ,                      | Вь             | ІВОДЫ ДЛЯ      | тестиро          | вания и             | исследов   | ания                 |                |           |

| BDUCC             | 37                       | 34                       | -              | -              | -                | -                   | , ,        |                      |                |           |

|         | Контактная            |            | T         | ип корпу  | ca              |         | Дополнительные функции вывода |          |         |          |

|---------|-----------------------|------------|-----------|-----------|-----------------|---------|-------------------------------|----------|---------|----------|

| Вывод   | площадка<br>кристалла | 4229.132-3 | H18.64-1B | H16.48-1B | MK<br>5153.64-2 | LQFP64  | Аналог.                       | Основ.   | Альтер. | Переопр. |

| EXT_POR | 39                    | 36         | -         | -         | -               | -       |                               |          |         | •        |

|         |                       |            |           |           |                 |         | <b>«</b>                      | <b>»</b> |         |          |

| SHDN    | 27                    | 24         | -         | -         | -               | -       |                               |          | /       |          |

|         |                       |            |           |           |                 |         |                               | LDO.     |         |          |

|         |                       |            |           |           |                 |         |                               |          |         |          |

|         |                       |            |           |           |                 |         | <b>«</b>                      | <b>»</b> |         |          |

| JTAG_EN | 102                   | 97         | -         | -         | -               | -       |                               |          |         |          |

|         |                       |            |           |           |                 |         | <b>«</b>                      | <b>»</b> |         |          |

|         |                       |            |           |           | Не испо         | льзуютс | Я                             |          |         |          |

| NC      | 23,24,                | 116,120    | 32        | 24        | 32              | 37      |                               |          |         |          |

|         | 117,118,              |            |           |           |                 |         | <b>«</b>                      | <b>»</b> |         |          |

|         | 126,127               |            |           |           |                 |         |                               |          |         |          |

\* - 1986 94 .

Таблица 3 — Описание выводов микроконтроллеров серии 1986BE9x в корпусах МК 6109.144-A, МК 8307.144-AH3

| вывода |

|--------|

|        |

|        |

|        |

| XT_BUS |

|        |

|        |

|        |

|        |

| XT_BUS |

|        |

|        |

|        |

|        |

| XT_BUS |

|        |

|        |

|        |

|        |

| XT_BUS |

|        |

|        |

|        |

|        |

| XT_BUS |

|        |

|        |

|        |

|                 | Обозна-      | Назначение и функции вывода |                            |                                  |          |              |          |            |  |  |  |

|-----------------|--------------|-----------------------------|----------------------------|----------------------------------|----------|--------------|----------|------------|--|--|--|

| Номер<br>вывода | чение вывода | Тип функции<br>вывода       | Обозначение функции вывода | Функциональное назначение вывода |          |              |          |            |  |  |  |

| <b>A</b> 4      | PA5          |                             | /                          | 5                                |          |              |          |            |  |  |  |

|                 |              |                             | -                          | -                                |          |              |          |            |  |  |  |

|                 |              |                             | DATA5                      | 5                                | DA       | ATA[3]       | 1:0] EXT | Γ_BUS      |  |  |  |

|                 |              |                             | TMR1_CH3                   | /                                | 3        | 1            |          |            |  |  |  |

|                 |              |                             | TMR2_CH3                   | /                                | 3        | 2            |          |            |  |  |  |

| 34              | PA6          |                             | /                          | 6                                |          |              |          |            |  |  |  |

|                 |              |                             | -  -                       | -                                |          |              |          |            |  |  |  |

|                 |              |                             | DATA6                      | 6                                | DA       | ATA[3        | 1:0] EXT | Γ_BUS      |  |  |  |

|                 |              |                             | CAN1_TX                    |                                  |          | C            | AN1      |            |  |  |  |

|                 |              |                             | UART1_RXD                  |                                  | UART1    |              |          |            |  |  |  |

| C4              | PA7          |                             | /                          | 7                                |          |              |          |            |  |  |  |

|                 |              |                             | <u> </u>                   |                                  |          |              |          |            |  |  |  |

|                 |              |                             | DATA7                      | 7                                | DA       | ATA[3        | 1:0] EXT | Γ_BUS      |  |  |  |

|                 |              |                             | CAN1_RX                    |                                  |          | CA           | .N1      |            |  |  |  |

|                 |              |                             | UART1_TXD                  |                                  | UART′    | 1            |          |            |  |  |  |

| C5 PA8          |              |                             |                            | 8                                |          |              |          |            |  |  |  |

|                 |              |                             | I_                         |                                  |          |              |          |            |  |  |  |

|                 |              |                             | DATA8                      | 8                                | DA       | ATA[3]       | 1:0] EXT | ΓBUS       |  |  |  |

|                 |              |                             | TMR1_CH3N                  |                                  |          | 3            | 1        |            |  |  |  |

|                 |              |                             | TMR2_CH3N                  |                                  |          | 3            | 2        |            |  |  |  |

| A5              | PA9          |                             |                            | 9                                |          |              |          |            |  |  |  |

|                 |              |                             | -  -                       |                                  |          |              |          |            |  |  |  |

|                 |              |                             | DATA9                      | 9                                | DA       | ATA[3        | 1:0] EX7 | ΓBUS       |  |  |  |

|                 |              |                             | TMR1_CH4                   | /                                | 4        | 1            | ,        |            |  |  |  |

|                 |              |                             | TMR2_CH4                   | 1                                | 4        | 2            |          |            |  |  |  |

| 35              | PA10         |                             | /                          | 10                               | •        |              |          |            |  |  |  |

|                 |              |                             |                            | -                                |          |              |          |            |  |  |  |

|                 |              |                             | DATA10                     | 10                               | Г        | ΔΤΔΓ         | 31:01 FX | T_BUS      |  |  |  |

|                 |              |                             | nUART1DTR                  |                                  |          | // 1 1 / 1[. | J1.0] L2 | UART1      |  |  |  |

|                 |              |                             | TMR2_CH4N                  |                                  |          | 4            | 2        | UAKII      |  |  |  |

| D5              | PA11         |                             | /                          | 11                               |          |              |          |            |  |  |  |

|                 |              |                             | ,<br>                      | - 11                             |          |              |          |            |  |  |  |

|                 |              |                             | DATA11                     | 11                               | r        | ) A T A [    | 21.01 EV | T_BUS      |  |  |  |

|                 |              |                             | nUART1RTS                  | 11                               | L        | /A I A[,     | UAF      |            |  |  |  |

|                 |              |                             | TMR2_BLK                   |                                  |          |              | 2        | <b>\11</b> |  |  |  |

| <b>D</b> 6      | PA12         |                             | TWIKZ_DEK                  | 12                               |          |              |          |            |  |  |  |

| <b>7</b> 0      |              |                             | /<br>                      |                                  |          |              |          |            |  |  |  |

|                 |              |                             | DATA12                     |                                  | <u> </u> | \ A TT A 5'  | 21.03.55 | T DIIC     |  |  |  |

|                 |              |                             |                            | 12                               | L        | ATA[.        | 51:UJ EX | T_BUS      |  |  |  |

|                 |              |                             | nUART1RI                   |                                  |          |              |          |            |  |  |  |

|                 |              |                             | TMR2_ETR                   |                                  |          |              | 2        |            |  |  |  |

|                        | Обозна-         | Назначение и функции вывода          |           |                                  |                    |  |  |  |  |

|------------------------|-----------------|--------------------------------------|-----------|----------------------------------|--------------------|--|--|--|--|

| <b>Номер</b><br>вывода | чение<br>вывода | Тип функции вывода Обозначени вывода |           | Функциональное назначение вывода |                    |  |  |  |  |

| A6                     | PA13            |                                      | /         | 13                               |                    |  |  |  |  |

|                        |                 |                                      |           |                                  |                    |  |  |  |  |

|                        |                 |                                      | DATA13    | 13                               | DATA[31:0] EXT_BUS |  |  |  |  |

|                        |                 |                                      | nUART1DCD |                                  |                    |  |  |  |  |

|                        |                 |                                      | TMR1_CH4N |                                  | 4 1                |  |  |  |  |

| 6                      | PA14            |                                      |           | 14                               |                    |  |  |  |  |

|                        |                 |                                      |           |                                  |                    |  |  |  |  |

|                        |                 |                                      | DATA14    | 14                               | DATA[31:0] EXT_BUS |  |  |  |  |

|                        |                 |                                      | nUART1DSR |                                  |                    |  |  |  |  |

|                        |                 |                                      | TMR1_BLK  |                                  | 1                  |  |  |  |  |

| 6                      | PA15            |                                      | /         | 15                               |                    |  |  |  |  |

|                        |                 |                                      | -  -      |                                  |                    |  |  |  |  |

|                        |                 |                                      | DATA15    | 15                               | DATA[31:0] EXT_BUS |  |  |  |  |

|                        |                 |                                      | nUART1CTS |                                  |                    |  |  |  |  |

|                        |                 |                                      | TMR1_ETR  |                                  | 1                  |  |  |  |  |

| Іорт В                 | <u>'</u>        |                                      |           |                                  |                    |  |  |  |  |

| D11                    | PB0/            |                                      | /         | 0                                | /                  |  |  |  |  |

|                        | JA_TDO          |                                      |           | JTAG-                            |                    |  |  |  |  |

|                        |                 |                                      | DATA16    | 16                               | DATA[31:0] EXT_BUS |  |  |  |  |

|                        |                 |                                      | TMR3_CH1  | /                                | 1 3                |  |  |  |  |

|                        |                 |                                      | UART1_TXD | 1                                | UART1              |  |  |  |  |

| D12                    | PB1/            |                                      | /         | 1                                | /                  |  |  |  |  |

|                        | JA_TMS          |                                      | ,         | JTA                              | .G                 |  |  |  |  |

|                        |                 |                                      |           |                                  | _                  |  |  |  |  |

|                        |                 |                                      | DATA17    | 17                               | DATA[31:0] EXT_BUS |  |  |  |  |

|                        |                 |                                      | TMR3_CH1N |                                  | 1 3                |  |  |  |  |

|                        |                 |                                      | UART2_RXD |                                  | UART2              |  |  |  |  |

| 9                      | PB2/            |                                      | /         | 2<br>JTAG                        | /                  |  |  |  |  |

|                        | JA_TCK          |                                      | _         | JIAU                             | _                  |  |  |  |  |

|                        |                 |                                      | DATA18    | 18                               | DATA[31:0] EXT_BUS |  |  |  |  |

|                        |                 |                                      | TMR3_CH2  |                                  | 2 3                |  |  |  |  |

|                        |                 |                                      | CAN1_TX   |                                  | CAN1               |  |  |  |  |

| C10                    | PB3/            |                                      | /         | 3                                | 1                  |  |  |  |  |

|                        | JA_TDI          |                                      |           | JTAG                             |                    |  |  |  |  |

|                        |                 |                                      | - DATA10  |                                  |                    |  |  |  |  |

|                        |                 |                                      | DATA19    | 19                               | DATA[31:0] EXT_BUS |  |  |  |  |

|                        |                 |                                      | TMR3_CH2N |                                  | 2 3<br>CAN1        |  |  |  |  |

| 111                    | PB4/            |                                      | CAN1_RX   | 4                                | / CANT             |  |  |  |  |

| 11                     | JA_TRST         |                                      | 1         | 4<br>JTAG                        | 1                  |  |  |  |  |

|                        |                 |                                      | [-        |                                  |                    |  |  |  |  |

|                        |                 |                                      | DATA20    | 20                               | DATA[31:0] EXT_BUS |  |  |  |  |

|                        |                 |                                      | TMR3_BRK  |                                  | 3                  |  |  |  |  |

|                        |                 |                                      | TMR3_ETR  |                                  | 3                  |  |  |  |  |

|                 | Обозна-      | Назначение и функции вывода |                            |                                  |                    |  |  |  |

|-----------------|--------------|-----------------------------|----------------------------|----------------------------------|--------------------|--|--|--|

| Номер<br>вывода | чение вывода | Тип функции<br>вывода       | Обозначение функции вывода | Функциональное назначение вывода |                    |  |  |  |

| <b>A</b> 10     | PB5          |                             | /                          | 5                                |                    |  |  |  |

|                 |              |                             | -                          | •                                |                    |  |  |  |

|                 |              |                             | DATA21                     | 21                               | DATA[31:0] EXT_BUS |  |  |  |

|                 |              |                             | UART1_TXD                  |                                  | UART1              |  |  |  |

|                 |              |                             | TMR3_CH3                   | /                                | 3 3                |  |  |  |

| 310             | PB6          |                             | /                          | 6                                |                    |  |  |  |

|                 |              |                             | <u> </u>                   |                                  |                    |  |  |  |

|                 |              |                             | DATA22                     | 22                               | DATA[31:0] EXT_BUS |  |  |  |

|                 |              |                             | UART1_RXD                  |                                  | UART1              |  |  |  |

|                 |              |                             | TMR3_CH3N                  |                                  | 3 3                |  |  |  |

| 39              | PB7          |                             | /                          | 7                                |                    |  |  |  |

|                 |              |                             | -  -                       | •                                |                    |  |  |  |

|                 |              |                             | DATA23                     | 23                               | DATA[31:0] EXT_BUS |  |  |  |

|                 |              |                             | nSIROUT1                   |                                  | IRDA SIR ART1      |  |  |  |

|                 |              |                             | TMR3_CH4                   | /                                | 4 3                |  |  |  |

| 19              | PB8          |                             | /                          | 8                                |                    |  |  |  |

|                 |              |                             |                            |                                  |                    |  |  |  |

|                 |              |                             | DATA24                     | 24                               | DATA[31:0] EXT_BUS |  |  |  |

|                 |              |                             | COMP_OUT                   |                                  |                    |  |  |  |

|                 |              |                             | TMR3_CH4N                  |                                  | 4 3                |  |  |  |

| D8              | PB9          |                             | /                          | 9                                |                    |  |  |  |

|                 |              |                             |                            | •                                |                    |  |  |  |

|                 |              |                             | DATA25                     | 25                               | DATA[31:0] EXT_BUS |  |  |  |

|                 |              |                             | nSIRIN1                    |                                  | IRDA SIR UART1     |  |  |  |

|                 |              |                             | EXT_INT4                   |                                  |                    |  |  |  |

| C8              | PB10         |                             |                            | 10                               |                    |  |  |  |

|                 |              |                             | -  -  -                    |                                  |                    |  |  |  |

|                 |              |                             | DATA26                     | 26                               | DATA[31:0] EXT_BUS |  |  |  |

|                 |              |                             | EXT_INT2                   |                                  |                    |  |  |  |

|                 |              |                             | nSIROUT1                   |                                  | IRDA SIR UART1     |  |  |  |

| 38              | PB11         |                             |                            | 11                               |                    |  |  |  |

|                 |              |                             | T_ T_                      |                                  |                    |  |  |  |

|                 |              |                             | DATA27                     | 27                               | DATA[31:0] EXT_BUS |  |  |  |

|                 |              |                             | EXT_INT1                   |                                  | 2[21.0] 2.11_000   |  |  |  |

|                 |              |                             | COMP_OUT                   |                                  |                    |  |  |  |

| 18              | PB12         |                             |                            | 12                               |                    |  |  |  |

|                 |              |                             |                            |                                  |                    |  |  |  |

|                 |              |                             | DATA28                     | 28                               | DATA[31:0] EXT_BUS |  |  |  |

|                 |              |                             | SSP1_FSS                   | /                                | SPI1               |  |  |  |

|                 |              |                             | SSP2_FSS                   | /                                | SPI2               |  |  |  |

| Номер<br>вывода | Обозна-         | Назначение и функции вывода |                            |                                  |                          |  |  |  |

|-----------------|-----------------|-----------------------------|----------------------------|----------------------------------|--------------------------|--|--|--|

|                 | чение<br>вывода | Тип функции<br>вывода       | Обозначение функции вывода | Функциональное назначение вывода |                          |  |  |  |

| 37              | PB13            |                             |                            | / 13                             |                          |  |  |  |

|                 |                 |                             | _                          | _                                |                          |  |  |  |

|                 |                 |                             | DATA29                     | 29                               | DATA[31:0] EXT_BUS       |  |  |  |

|                 |                 |                             | SSP1_CLK                   | 1                                | SPI1                     |  |  |  |

|                 |                 |                             | SSP2_CLK                   | /                                | SPI2                     |  |  |  |

| .7              | PB14            |                             | T                          | / 14                             |                          |  |  |  |

|                 |                 |                             | -<br> DATA20               | _                                |                          |  |  |  |

|                 |                 |                             | DATA30                     | 30                               | DATA[31:0] EXT_BUS       |  |  |  |

|                 |                 |                             | SSP1_RXD                   |                                  | SPI1                     |  |  |  |

| 77              | PB15            |                             | SSP2_RXD                   | 1 45                             | SPI2                     |  |  |  |

| 27              | PB15            |                             |                            | / 15<br>I                        |                          |  |  |  |

|                 | <u></u>         |                             | DATA21                     | 31                               | DATA[21.0] EVE DUC       |  |  |  |

|                 |                 |                             | DATA31<br>SSP1_TXD         | 31                               | DATA[31:0] EXT_BUS  SPI1 |  |  |  |

|                 |                 |                             | SSP2_TXD                   |                                  | SPI2                     |  |  |  |

| Торт С          |                 |                             | 33F 2_T XD                 |                                  | JF12                     |  |  |  |

| D10             | PC0             |                             |                            | / 0                              |                          |  |  |  |

|                 |                 |                             |                            | ,                                |                          |  |  |  |

|                 |                 |                             | _                          |                                  |                          |  |  |  |

|                 |                 |                             | SCL1                       |                                  | I2C                      |  |  |  |

|                 |                 |                             | SSP2_FSS                   | /                                | SPI 2                    |  |  |  |

| E10             | PC1             |                             |                            | / 1                              | -                        |  |  |  |

|                 |                 |                             |                            | _                                |                          |  |  |  |

|                 |                 |                             | OE                         |                                  |                          |  |  |  |

|                 |                 |                             | SDA1                       | EXT_BUS                          | I2C                      |  |  |  |

|                 | <u></u>         |                             | SSP2_CLK                   | /                                | SPI2                     |  |  |  |

| E12             | PC2             |                             | 331 2_CLK                  | / 2                              | 31 1Z                    |  |  |  |

|                 |                 |                             |                            | / <u> </u>                       |                          |  |  |  |

|                 |                 |                             | WE                         |                                  |                          |  |  |  |

|                 |                 |                             | TMR3_CH1                   | EXT_BUS                          |                          |  |  |  |

|                 |                 |                             |                            | /                                | 1 3                      |  |  |  |

| E11             | PC3             |                             | SSP2_RXD                   | / 0                              | SPI2                     |  |  |  |

| 211             | PC3             |                             |                            | / 3                              |                          |  |  |  |

|                 |                 |                             | BE0                        | <del>-</del>                     | 0 32                     |  |  |  |

|                 |                 |                             |                            |                                  | EXT_BUS                  |  |  |  |

|                 |                 |                             | TMR3_CH1N                  |                                  | 1 3                      |  |  |  |

|                 |                 |                             | SSP2_TXD                   |                                  | SPI2                     |  |  |  |

| E9              | PC4             |                             | T                          | / 4                              |                          |  |  |  |

|                 |                 |                             | -<br> DE1                  | _                                |                          |  |  |  |

|                 |                 |                             | BE1                        |                                  | 1 32<br>EXT_BUS          |  |  |  |

|                 |                 |                             | TMR3_CH2                   | /                                | 2 3                      |  |  |  |

|                 |                 |                             | TMR1_CH1                   | /                                | 1 1                      |  |  |  |

|                 | Обозна-<br>чение<br>вывода | Назначение и функции вывода |                            |       |              |         |             |  |

|-----------------|----------------------------|-----------------------------|----------------------------|-------|--------------|---------|-------------|--|

| Номер<br>вывода |                            | Тип функции<br>вывода       | Обозначение функции вывода | Функц | циональное і | іазначе | ение вывода |  |

| F9              |                            |                             |                            |       |              |         |             |  |

|                 |                            |                             | BE2                        |       | EXT_BUS      | 2 32    |             |  |

|                 |                            |                             | TMR3_CH2N                  |       | EA1_BUS      | 2       | 3           |  |

| 71.0            | DG (                       |                             | TMR1_CH1N                  |       |              | 1       | 1           |  |

| F12             | PC6                        |                             | /<br> -<br> -              | -     |              |         |             |  |

|                 | ••••                       |                             | BE3                        |       | EXT_BUS      | 3 32    |             |  |

|                 |                            |                             | TMR3_CH3                   | /     | 3            | 3       |             |  |

|                 |                            |                             | TMR1_CH2                   | 1     | 2            | 1       |             |  |

| F11             | PC7                        |                             | 1                          | 7     |              |         |             |  |

|                 |                            |                             |                            | -     |              |         |             |  |

|                 |                            |                             | CLOCK                      |       | EX           | T_BUS   | 3           |  |

|                 |                            |                             | TMR3_CH3N                  |       |              | 3       | 3           |  |

|                 |                            |                             | TMR1_CH2N                  |       |              | 2       | 1           |  |

| F10             | PC8                        |                             | 1                          | 8     |              |         |             |  |

|                 |                            |                             | -  -                       | _     |              |         |             |  |

|                 |                            |                             | CAN1_TX                    |       |              | С       | AN1         |  |

|                 | <br>                       |                             | TMR3_CH4                   | /     | 4            | 3       |             |  |

|                 |                            |                             | TMR1_CH3                   | 1     | 3            | 1       |             |  |

| G10             | PC9                        |                             | /                          | 9     |              |         |             |  |

|                 |                            |                             | [ <u> </u>                 | _     |              |         |             |  |

|                 |                            |                             | CAN1_RX                    |       |              | CA      | .N1         |  |

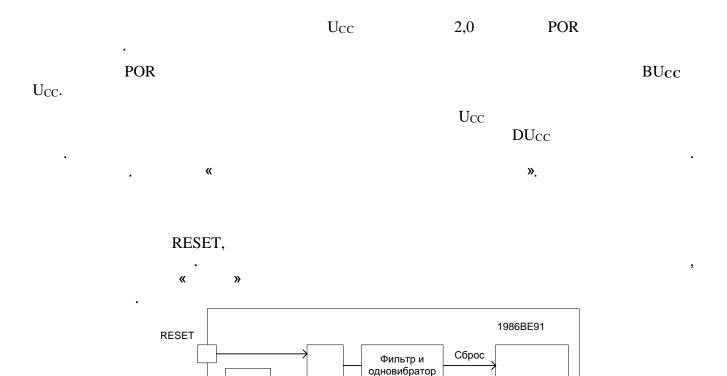

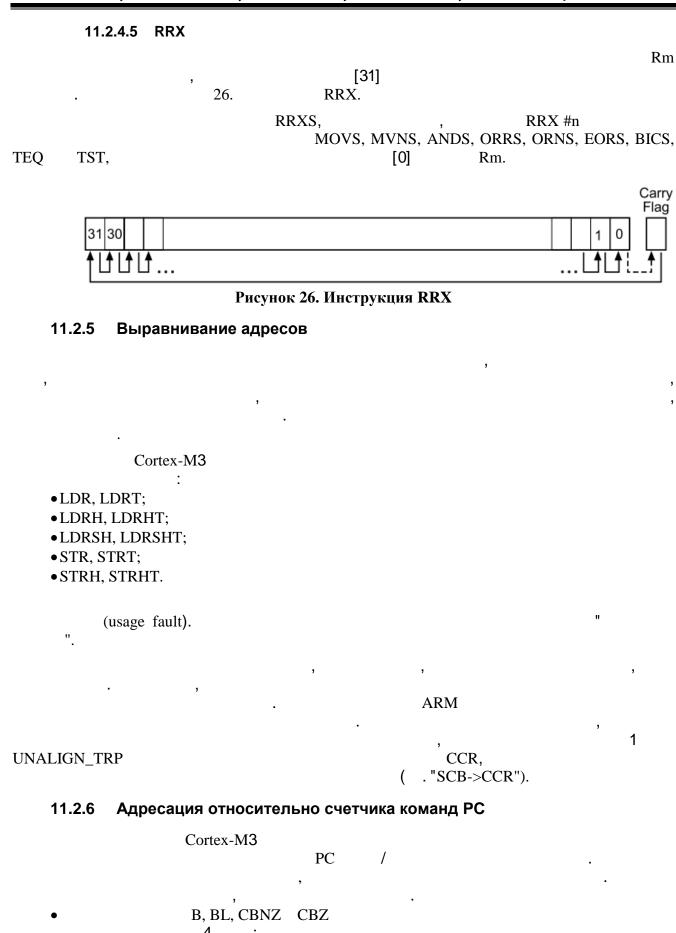

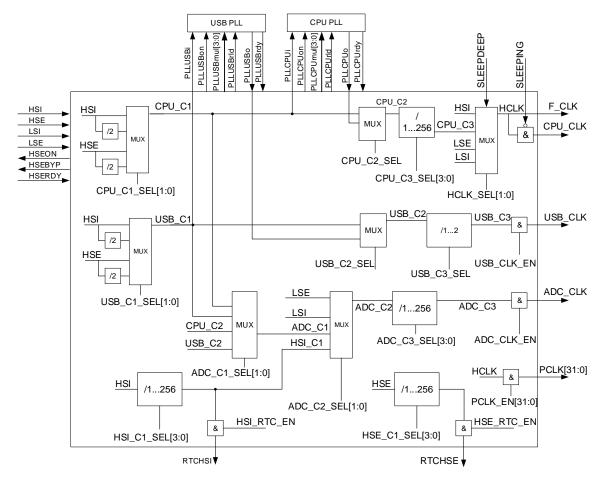

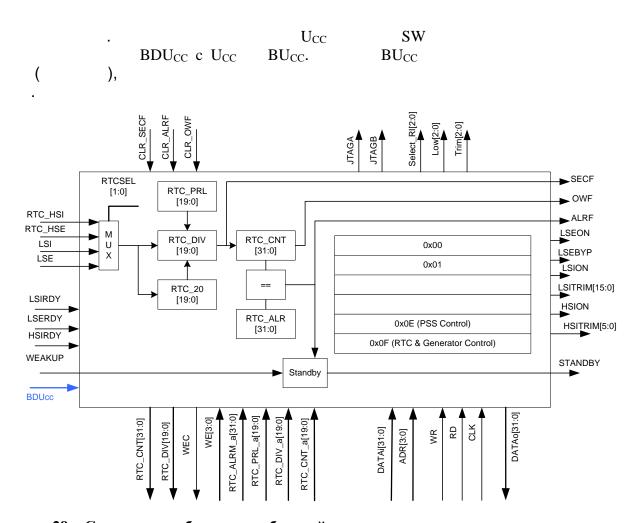

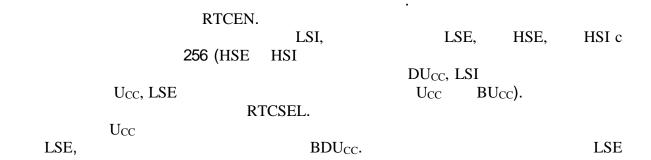

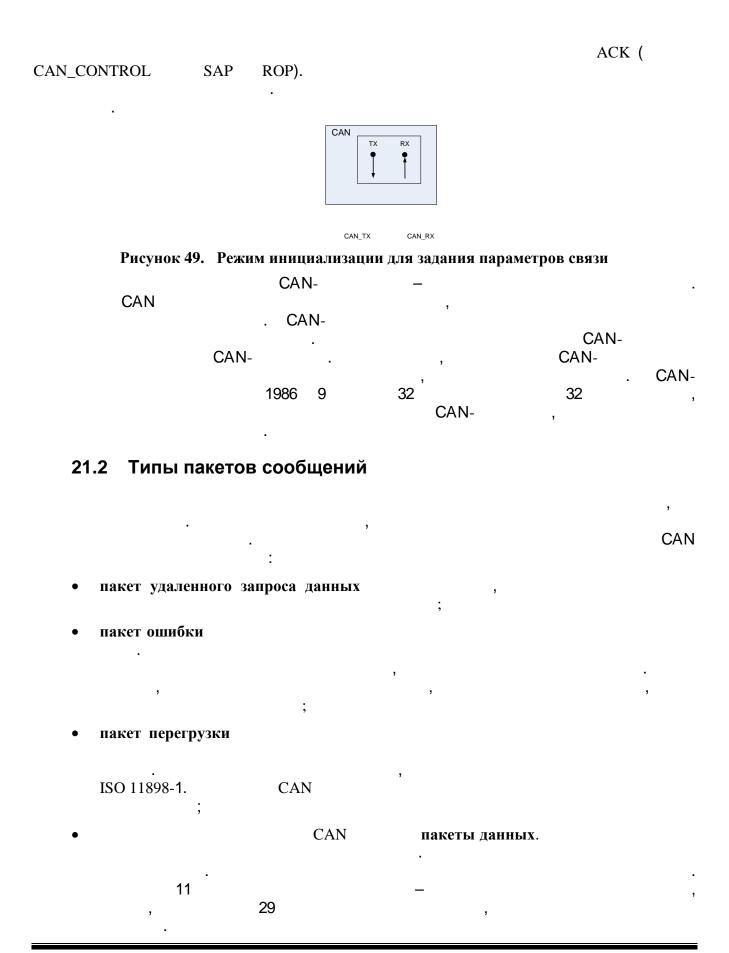

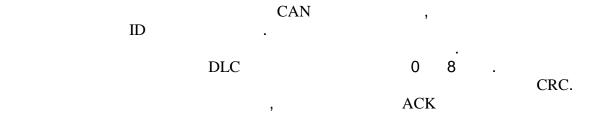

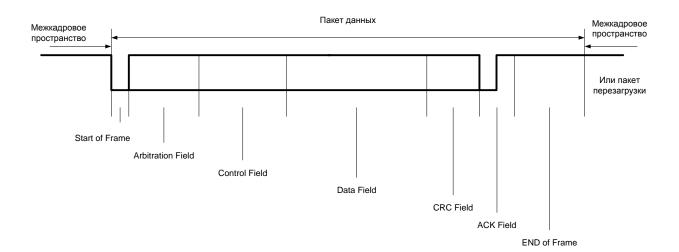

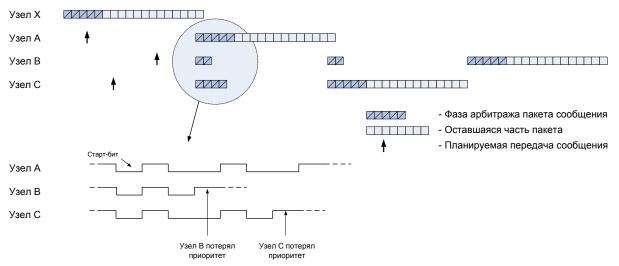

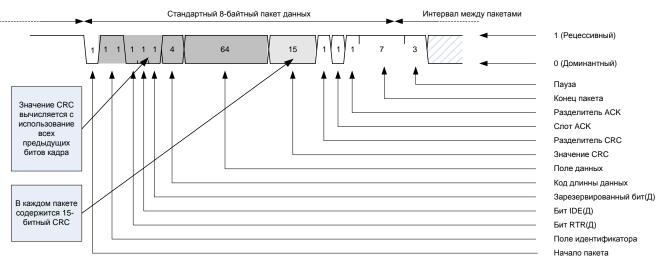

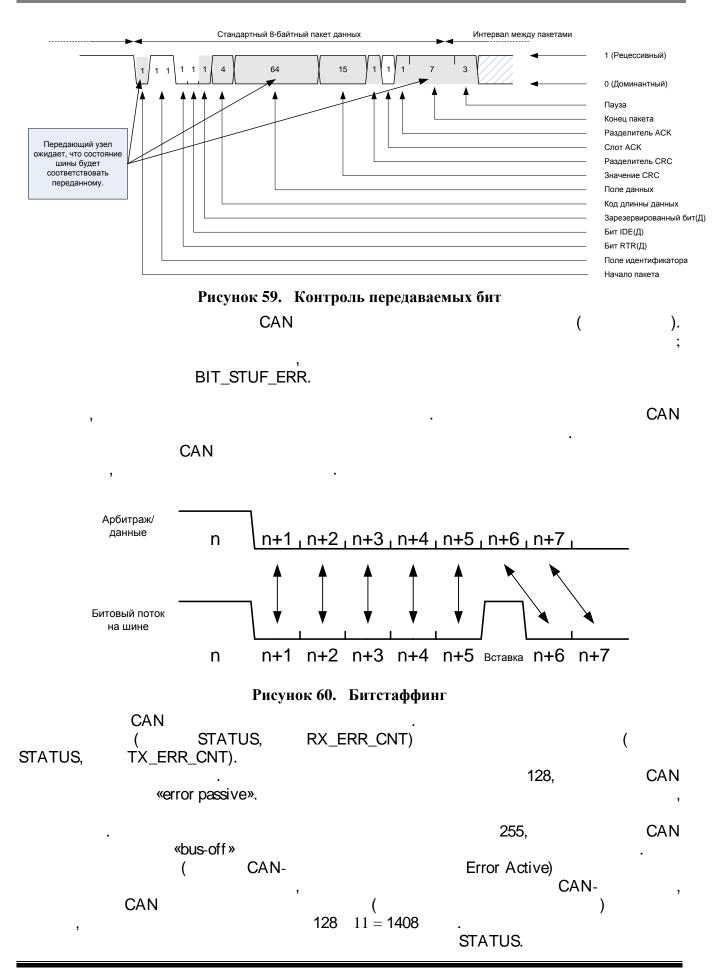

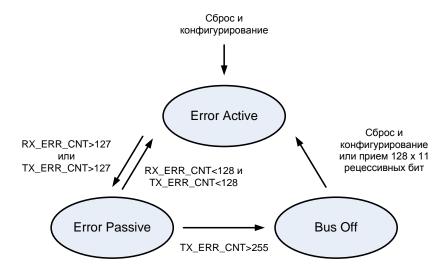

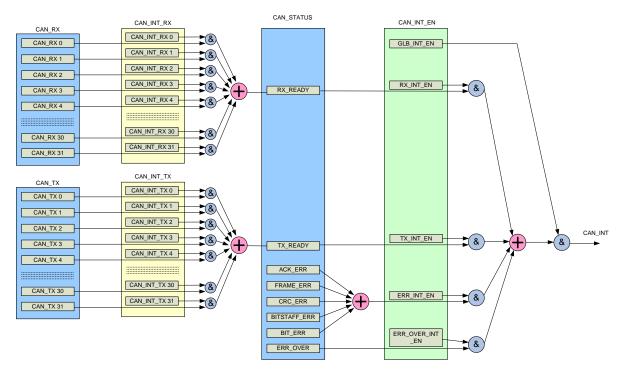

|                 |                            |                             | TMR3_CH4N                  |       |              | 4       | 3           |  |